## Self aligned hysteresis free carbon nanotube field-effect transistors

M. Shlafman, T. Tabachnik, O. Shtempluk, A. Razin, V. Kochetkov, and Y. E. Yaish

Citation: Applied Physics Letters **108**, 163104 (2016); doi: 10.1063/1.4947099 View online: http://dx.doi.org/10.1063/1.4947099 View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/108/16?ver=pdfcov Published by the AIP Publishing

## Articles you may be interested in

Stable doping of carbon nanotubes via molecular self assembly J. Appl. Phys. **116**, 144503 (2014); 10.1063/1.4897550

High performance transistors via aligned polyfluorene-sorted carbon nanotubes Appl. Phys. Lett. **104**, 083107 (2014); 10.1063/1.4866577

All-printed and transparent single walled carbon nanotube thin film transistor devices Appl. Phys. Lett. **103**, 143303 (2013); 10.1063/1.4824475

Carbon nanotube-ZnO nanowire hybrid architectures as multifunctional devices AIP Advances **3**, 082106 (2013); 10.1063/1.4817837

Oxygen plasma post process to obtain consistent conductance of carbon nanotubes in carbon nanotube fieldeffect transistors Appl. Phys. Lett. **101**, 173104 (2012); 10.1063/1.4762829

## Self aligned hysteresis free carbon nanotube field-effect transistors

M. Shlafman, T. Tabachnik, O. Shtempluk, A. Razin, V. Kochetkov, and Y. E. Yaish<sup>a</sup> Andrew and Erna Viterbi Faculty of Electrical Engineering, Technion, Haifa 32000, Israel

(Received 4 February 2016; accepted 21 March 2016; published online 20 April 2016)

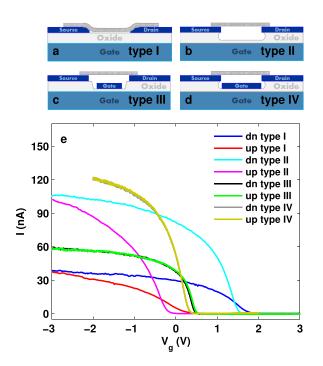

Hysteresis phenomenon in the transfer characteristics of carbon nanotube field effect transistor (CNT FET) is being considered as the main obstacle for successful realization of electronic devices based on CNTs. In this study, we prepare four kinds of CNTFETs and explore their hysteretic behavior. Two kinds of devices comprise on-surface CNTs (type I) and suspended CNTs (type II) with thin insulating layer underneath and a single global gate which modulates the CNT conductance. The third and fourth types (types III and IV) consist of suspended CNT over a metallic local gate underneath, where for type IV the local gate was patterned self aligned with the source and drain electrodes. The first two types of devices, i.e., type I and II, exhibit substantial hysteresis which increases with scanning range and sweeping time. Under high vacuum conditions and moderate electric fields ( $|E| > 4 \times 10^6 \text{ V/cm}$ ), the hysteresis for on-surface devices cannot be eliminated, as opposed to suspended devices. Interestingly, type IV devices exhibit no hysteresis at all at ambient conditions, and from the different roles which the global and local gates play for the four types of devices, we could learn about the hysteresis mechanism of this system. We believe that these self aligned hysteresis free FETs will enable the realization of different electronic devices and sensors based on CNTs. *Published by AIP Publishing*. [http://dx.doi.org/10.1063/1.4947099]

For more than a decade, single-wall carbon nanotubes (CNTs) have been considered as realistic alternative for conventional transistors.<sup>1–6</sup> Substantial efforts were devoted for either growing or positioning the tubes at specific locations for functional operations.<sup>7–12</sup> Other efforts demonstrated different electrical components, such as inverters, memory cells, and logic circuits based solely on CNTs.<sup>13–16</sup> One may assume that full integration of CNTs within silicon technology can be realized in few years. However, for efficient operation of any commercial electronic circuit each component should have reproducible electrical performance and low noise level. Due to the superb sensitivity of CNTs to their external environment, these two crucial requirements are far from being fulfilled.

On-surface CNTs are known to suffer from low signal to noise ratio (SNR) due to charged traps within the insulating medium, and fabrication residues, such as PMMA and photoresist.<sup>14,15,17–21</sup> Suspended CNTs have much higher SNR, especially if are grown at the last step of the fabrication process.<sup>22,23</sup> Yet, these suspended CNTs exhibit significant hysteresis in their transfer characteristics at ambient conditions, which depends on the scan rate and on the gate voltage range.<sup>24–27</sup> Commercial application such as chemical sensing,<sup>28,29</sup> which is considered as one of the most attractive applications of CNT field effect transistors (FETs), suffers dramatically from this phenomenon. The effective electric potential that governs the tube conductance tends to drift with time and a significant reduction of the device transconductance, and hence its sensitivity, occurs.

It was argued that few monolayers of water are responsible for this hysteresis. In a recent study, Pascal-Levy *et al.*<sup>25,27</sup> reported that these monolayers of water on the oxide film assist back gate (i.e., global gate) screening by

mobile charges, and behave as resistor-capacitor (RC) circuit,<sup>30</sup> with relaxation time which is inversely proportional to the oxide conductivity. This phenomenon causes retardation in the electrostatic environment which affects the CNT conductance and results in an uncontrollable hysteresis in the CNT transfer characteristics. Several studies have tried to minimize the hysteresis window, but none of them succeeded to eliminate it completely at ambient conditions.<sup>22,31–34</sup> In this letter, we present an alternative device geometry, based on a self aligned local metallic gate, which overcomes this obstacle, and achieves hysteresis free CNT FETs at ambient conditions. We describe the influence of the global and the local gates when they are gated separately, and when they are swept together in order to obtain deeper understanding of the hysteresis phenomenon.

In this study, four types of CNT FETs were prepared utilizing the growth at the end technique<sup>22,23</sup> in order to avoid any process residual contamination. One kind of devices (type I) comprises on-surface CNTs, and the other three comprise suspended tubes. Types I and II devices have thin insulating layer (SiO<sub>2</sub>) underneath the CNTs and a single global gate which modulates the CNT conductance. Types III and IV consist of suspended CNTs over a metallic local gate underneath, where for type IV the local gate was patterned self aligned with the source and drain (SD) electrodes.

The processing was performed on 500 nm SiO<sub>2</sub> thermally grown on highly p-doped silicon substrate, using only photolithography techniques. First, SD were patterned with 5/40 nm Cr/Pt electrodes, with gaps of 1.3/1.8  $\mu$ m between SD. Next, three types of trenches were fabricated. For types II and IV, 400 nm and 100 nm deep trenches were etched in 1:6 buffer oxide etch (BOE) for four and one minutes, respectively. For type III, the 400 nm trench was prepared by reactive ion etching (RIE). For types III and IV, additional lithography step was involved in order to deposit a thin

a)Electronic mail: yuvaly@ee.technion.ac.il

metallic electrode (5/40 nm Cr/Pt) within the trench in between the SD electrodes (see Figs. 1(a)-1(d)). This metallic electrode serves as a local gate for types III and IV CNT FETs. For type IV, this lithography step included overlap of the local gate with the metallic SD electrodes resulting in a self aligned configuration. Finally (for all the devices), ferritin solution was deposited at specific places, and the CNTs were grown by chemical vapor deposition (CVD) with methane/hydrogen gas mixture (0.5/0.5 SLM) at 900 °C.<sup>25,27</sup>

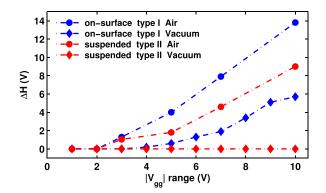

Fig. 1(e) in the main text and Fig. S1 in the supplementary material<sup>35</sup> depict the transfer characteristics of CNT FETs in linear and logarithmic scales, respectively, one from each type (Figs. 1(a)-1(d)). All the measured devices comprise semiconducting CNTs with I<sub>ON</sub> /I<sub>OFF</sub> ratios larger than 10<sup>2</sup>. From the linear part of the  $I-V_g$  curve (Fig. 1(e)), the linearly extrapolated crossing point  $(V_{on})$  with the  $V_g$  axis (zero current) was measured, and the threshold voltage was extracted according to the following relation,<sup>36</sup>  $V_{th} = V_{on} - V_{ds}/2$ . For each sweeping direction, we obtained the respective threshold voltage, and the difference between the two values is noted as the hysteresis window,  $\Delta H$ . At ambient conditions, type I and II CNT FETs exhibit an advanced hysteresis (counter clock wise - CCW, Fig. 1(e)). This hysteresis depends on the humidity level, gate voltage ranges, and sweep rates. Example for this behavior is presented in Fig. 2 where  $\Delta H$  is plotted versus the different scanning ranges of the global gate voltage ( $|V_{gg}|$ ) for both on-surface (I) and suspended (II) CNT FETs. At ambient conditions and humidity level of 60%, both I and II CNTs display an increase of the hysteresis window as the applied voltage range increases. However, at high vacuum

FIG. 1. Schematic diagrams of the four types of devices that were tested. (a), (b) On-surface (type I), or suspended (type II) CNTs with global gate, (c), (d) suspended CNTs with local gate (type III), or self aligned local gate (type IV) and global gates (for both III and IV), (e) transfer characteristics of type I (blue line-down, red line-up), type II (light blue line-down, magenta line-up), type III (black line-down, green line-up), and type IV (gray line-down, yellow line-up) CNT FETs. The curves were measured at ambient conditions, humidity level of 60%, and bias (V<sub>ds</sub>) of 10 mV.

FIG. 2. Hysteresis window versus global gate sweeping ranges. Blue (red) circles present  $\Delta H$  for type I (II) devices measured at ambient conditions with 60% humidity level. Blue (red) diamonds present  $\Delta H$  for type I (II) devices measured at high vacuum (<10<sup>-5</sup> Torr).

conditions ( $<10^{-5}$  Torr) where water vapor is absent, different behavior is found. At low gate sweeping ranges ( $|V_{gg}| < 3$  V) which are equivalent to low up to moderate electric fields ( $|E| < E_{cr} = 4 \times 10^6$  V/cm), both types I and II devices exhibit no hysteresis in their transfer characteristics. However, as the sweeping voltage range increases, hysteresis of I starts to develop as opposed to II where no hysteresis is visible for the whole sweeping range.

The reason is the following: at low gate sweeping ranges and ambient conditions, the source of hysteresis is few monolayers of water which adsorb to the oxide surface and assist charges redistribution in response to the external gate voltage. When vacuum is introduced, water vapor disappears and no hysteresis prevails. However, for higher sweeping ranges, charges can tunnel between the CNT and the oxide traps and the hysteresis reappears. For suspended tubes, this back and forth tunneling is prevented, and no hysteresis is possible. This fundamental result states that even if one passivates a CNT FET beside the reduction of the SNR of the outcome device, the hysteresis will reappear at moderate and high electric fields.

Hence, hysteresis free CNT FETs, which typically operate at moderate and high electric fields, can not rely on onsurface devices but only on suspended ones. However, at ambient conditions even the suspended CNT devices suffer from hysteresis, as evident from previous studies and Figs. 1(e) and 2. Since the source of hysteresis for suspended CNTs originates from water assisted surface charge redistribution on top of the oxide layer, and because the hysteresis time constant of the equivalent resistor-capacitor (RC) circuit is proportional to  $1/\sigma_{ox}$ , where  $\sigma_{ox}$  is the oxide surface electrical conductivity,<sup>25,27</sup> an alternative device layout should be considered. Two architecture alternatives are types III and IV devices, where the CNT is suspended not over an oxide surface but rather over a local metallic gate. Figs. 1(e) and S1<sup>35</sup> depict the transfer characteristics of these devices as well (types III and IV), and clearly a substantial improvement in  $\Delta H$  is observed. Type III device shows significant reduction of the hysteresis, and for device IV it is completely eliminated.

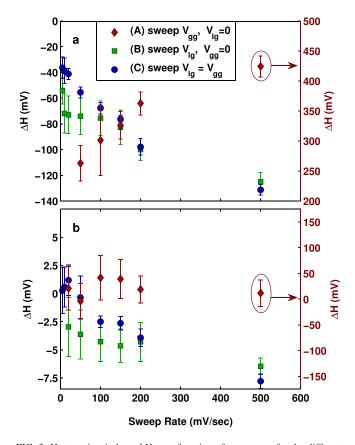

Interestingly, the hysteresis window and direction (clock wise (CW) or CCW) depend on the role of the local and the global gates during the measurements. In previous

reports,<sup>25,27</sup> we have confirmed that different sweep rates sample the temporal evolution of the hysteresis. Thus, in order to study further the influence of the metallic gates, we measure the hysteresis window at different sweep rates for different setups of the local and global gates. Fig. 3 depicts the results of these measurements. In order to present CCW and CW hysteresis in the same plot, we denote CCW hysteresis as positive ( $\Delta H > 0$ , advanced hysteresis<sup>25</sup>) and CW hysteresis as negative ( $\Delta H < 0$ , retarded hysteresis<sup>37</sup>). The red symbols present the hysteresis window when one sweeps  $V_{gg}$  and  $V_{lg} = 0$  (right axis). The green symbols present the hysteresis window when one sweeps  $V_{lg}$  and  $V_{gg} = 0$  (left axis). We denote these two configurations A and B, respectively. The blue symbols correspond to measurements where the two metallic gates were connected and swept together (configuration C, left axis). First, we notice that for types III and IV, the resulting  $\Delta H$  for the three tested configurations is substantially smaller than those depicted in Figs. 1(e) and 2 for device types I and II. Second, as was mentioned before, configuration C yields the minimal  $|\Delta H|$  for both III and IV, which vanishes completely for type IV device at low sweep rates. Additionally,  $\Delta H < 0$  (CW) for configurations B and *C*, and  $\Delta H > 0$  (CCW) for *A*.

Careful examination reveals the following observations: (a) minimizing the exposed oxide surface in the vicinity of the CNT reduces  $|\Delta H|$ ; (b) reducing the electrostatic coupling between the global gate and the CNT decreases the hysteresis

FIG. 3. Hysteresis window,  $\Delta H$ , as a function of sweep rate for the different device types and configurations. The different symbols for the different device configurations are marked in the figure legends. (a)  $\Delta H$  for device type III: configuration *A* (red) - right axis (red), configurations *B* (green) and *C* (blue) - left axis. (b)  $\Delta H$  for device type IV: configuration *A* (red) - right axis (red), configurations *B* (green) and *C* (blue) - left axis.

window. In order to elucidate the last point, we measure the mutual capacitance between the global (local) gate and the tube  $C_{gg}(C_{lg})$  for device types III and IV. Fig. S2a(b)<sup>35</sup> depicts the conductance (G) of a CNT as function of both  $V_{lg}$  (x-axis) and  $V_{gg}$  (y-axis) for device type III(IV). The ratio  $C_{lg}/C_{gg}$  is extracted from the slops of equi-conductance contours (white dashed lines). As expected, for device type III this ratio is  $\approx$ 5, where for device type IV it is much larger, approaching  $\approx$ 74.

This substantial difference between the two capacitance ratios can be easily understood from the three insets of Fig. S2.<sup>35</sup> The inset of Fig. S2(a)<sup>35</sup> presents scanning electron microscopy (SEM) image of type III fabricated device. The local gate is located between the two upper and lower SD electrodes and a faint CNT is bridging the gap over the predefined trench. As observed, two narrow oxide rims are located between the local gate and the two electrodes. The electric field originated from the global gate is screened by the metallic local gate, but not entirely due to the two oxide rims. As a consequence, the mutual capacitance between the global gate and the tube  $(C_{gg})$  is not negligible. However, the case for type IV is different. The right inset of Fig. S2(b)<sup>35</sup> presents a top view of an SEM image of type IV device and a CNT bridging the gap (yellow arrow). Clearly, the two earlier mentioned oxide rims are absent, and the local gate spans over the entire trench area up to the SD electrodes. The left inset presents an SEM image of the cross section of a cleaved device. From this image, we can see that the metallic local gate is indeed self aligned with the two SD electrodes, and its edges lay underneath both electrodes without causing any shorts. This alignment is responsible for the almost complete screening of the global gate by the metallic local gate and to the high capacitance ratio of this device type.

Next, we address the physical mechanisms for the hysteresis phenomenon as implied from our data. As previously discussed, moisture is responsible for the hysteresis phenomenon in device types I and II. For device type III, two sources for the  $\Delta H$  exist: (a) narrow oxide rims that can adsorb moisture which give rise to CCW hysteresis similar to I and II (which increases with reducing the sweep rate of the global gate), and (b) charge tunneling between shallow traps within the oxide layer and the adjacent metallic local gate edges.<sup>37</sup> For configuration A, in which the local gate is grounded and the sweeping voltage is applied to the global gate, strong electric fields exist between the two gates and charge tunneling between the local gate and the oxide traps is enabled.<sup>38</sup> These traps cause CCW hysteresis which decreases with reducing the sweep rate. The lifetime of electrons within the shallow traps is short and for slow sweep rates, the charge imbalance between upwards and downwards sweeping gate voltage is much smaller than for faster sweep rates. The data of the A configuration in Fig. 3(a) support the second mechanism as the dominant contribution for  $\Delta H$ . On the other hand, few other devices of type III exhibit the dominance of the first mechanism. For such cases, the  $\Delta H > 0$  (CCW) and increases with slower sweep rates.

For configuration *B*, in which the global gate is grounded and the local gate is swept, similar charge tunneling processes are feasible; however, this time they contribute CW hysteresis for type III devices. In configuration *A*, the sweeping voltage ( $V_{gg}$ ) is below the oxide traps, resulting in

CCW hysteresis, where for the *B* configuration the sweeping voltage  $(V_{lg})$  is above these traps, resulting in CW hysteresis. In this configuration, the moisture mediated hysteresis is significantly reduced due to the fact that surface charge redistribution is much less effective in screening the electric fields originated from the local gate as opposed to strong screening efficiency in configuration A. Indeed, the data of the B configuration in Fig. 3(a) reflect CW hysteresis, however, approximately four times smaller in magnitude than the same data for A. This reduction in the hysteresis window is attributed to the stronger electrostatic coupling of the local gate to the tube in comparison to the global gate  $(C_{lg}/C_{gg} \approx 5)$ . In an attempt to eliminate these charge tunneling processes, one should impose the same electrical potential on the two metallic gates, i.e.,  $V_{gg} = V_{lg}$  (configuration C). Indeed, it results in the lowest  $|\Delta H|$  among the three studied configurations for device type III. Although the hysteresis window for C is very small at low sweep rates, it does not disappear completely. This small residual hysteresis originates from charge transfer between the metallic local gate and the oxide traps as a consequence of the high electric fields which exist between the local gate and the SD electrodes.

Type IV device was designed in order to overcome these obstacles. The self aligned local gate eliminates any oxide rims adjacent to it, and disables any influence of charge tunneling as a consequence of electrical potential differences between the local gate and the SD electrodes for configuration C. A direct consequence of this configuration is an almost perfect screening of the global gate by the metallic local gate, as evident from the high capacitance ratio  $C_{lg}$ /  $C_{gg} \approx 74$  (Fig. S2(b)<sup>35</sup>). As expected, all of the three configurations (A, B, and C) yield much smaller  $|\Delta H|$  in comparison to their analogs in device type III. Even though it is CW for C, it is merely a consequence of the measurement setup  $(\Delta H \approx \nu \times \tau)$ , where  $\nu$  is the sweep rate in mV/s and  $\tau \approx 30 \,\mathrm{ms}$  is the integration time constant of the measurement setup. This additional hysteresis window is always negative and can be reduced completely by lowering the sweep rate and/or reducing the measurement time constant). Hence, we can safely claim that below sweep rate of 200 mV/s,  $|\Delta H| < 5 \,\mathrm{mV}$ , and practically disappears completely as the sweep rate reduces. These results are superior to those presented by Cao et al.<sup>22</sup> and Muoth et al.<sup>31</sup> In Ref. 22, the authors fabricated similar structure to device type IV; however, they succeeded to eliminate completely the hysteresis window only at specific environments, such as dry air, argon, or vacuum, and not in ambient conditions. In Ref. 31, the authors developed a complex fabrication process of CNT FETs which involved shadow mask evaporations and needle like formation of the electrical contacts to the CNTs. However, the resulted CNTs were quite resistive and the smallest measured hysteresis window was  $\Delta H = 8 \pm 5 \text{ mV}$  at 4 mV/s. Our fabrication method is much simpler, easy to scale-up, and results in vanishing of the hysteresis window even for much larger sweep rates.

In summary, four types of devices were presented in order to elucidate the dominant hysteresis mechanisms of CNT FETs. Type I comprises on-surface CNT, and type II comprises suspended CNT. Both types have single global gate and SiO<sub>2</sub> layer underneath the CNTs. Types III and IV comprise suspended CNTs as well but over a predefined local metallic gate additionally to the global back gate. For type IV, the local metallic gate was patterned self aligned with the SD electrodes. At ambient conditions, device types I and II exhibit substantial hysteresis window ( $\Delta H$ ) which cannot be eliminated. The main source for the hysteresis phenomenon is water assisted mobile charge redistribution on top of the oxide layer. Hence, utilizing local metallic gates should diminish this effect substantially, as measured by device types III and IV. However, due to charged traps within the oxide layer in the vicinity of the local metallic gate edges additional source of hysteresis prevails and prohibits complete elimination of  $\Delta H$ . Device type IV overcomes this obstacle and the resulted  $\Delta H$  vanishes.

We believe that device type IV which succeeds to overcome all the mentioned obstacles can serve as essential prototype for ultra sensitive chemical sensors and alternative electrical devices based on CNT FETs.

The authors thank the Russell Berrie Nanotechnology Institute, the Micro Nano Fabrication Unit at the Technion, and the Ministry of Industry, Trade and Labor via the MAGNET program (NES consortium) for support.

- <sup>1</sup>P. L. McEuen, M. S. Fuhrer, and H. K. Park, IEEE Trans. Nanotechnol. **1**, 78 (2002).

- <sup>2</sup>H. J. Dai, Acc. Chem. Res. 35, 1035 (2002).

- <sup>3</sup>P. Avouris, Z. Chen, and V. Perebeinos, Nat. Nanotechnol. 2, 605 (2007).

- <sup>4</sup>Q. Cao and J. A. Rogers, Adv. Mater. **21**, 29 (2009).

- <sup>5</sup>L.-M. Peng, Z. Zhang, and S. Wang, Mater. Today **17**, 433 (2014).

- <sup>6</sup>G. S. Tulevski, A. D. Franklin, D. Frank, J. M. Lobez, Q. Cao, H. Park, A. Afzali, S.-J. Han, J. B. Hannon, and W. Haensch, ACS Nano 8, 8730 (2014).

- <sup>7</sup>J. Kong, H. T. Soh, A. M. Cassell, C. F. Quate, and H. J. Dai, Nature **395**, 878 (1998).

- <sup>8</sup>S. M. Huang, B. Maynor, X. Y. Cai, and J. Liu, Adv. Mater. **15**, 1651 (2003).

- <sup>9</sup>A. Ismach, L. Segev, E. Wachtel, and E. Joselevich, Angew. Chem., Int. Ed. 43, 6140 (2004).

- <sup>10</sup>C. Kocabas, S. H. Hur, A. Gaur, M. A. Meitl, M. Shim, and J. A. Rogers, Small 1, 1110 (2005).

- <sup>11</sup>A. Vijayaraghavan, S. Blatt, D. Weissenberger, M. Oron-Carl, F. Hennrich, D. Gerthsen, H. Hahn, and R. Krupke, Nano Lett. 7, 1556 (2007).

- <sup>12</sup>E. Penzo, M. Palma, D. A. Chenet, G. Ao, M. Zheng, J. C. Hone, and S. J. Wind, ACS Nano 10(2), 2975–2981 (2016).

- <sup>13</sup>V. Derycke, R. Martel, J. Appenzeller, and P. Avouris, Nano Lett. 1, 453 (2001).

- <sup>14</sup>M. S. Fuhrer, B. M. Kim, T. Drkop, and T. Brintlinger, Nano Lett. 2, 755 (2002).

- <sup>15</sup>M. Radosavljevic, M. Freitag, K. V. Thadani, and A. T. Johnson, Nano Lett. 2, 761 (2002).

- <sup>16</sup>M. M. Shulaker, G. Hills, N. Patil, H. Wei, H.-Y. Chen, H. S. PhilipWong, and S. Mitra, Nature 501, 526 (2013).

- <sup>17</sup>A. Robert-Peillard and S. Rotkin, IEEE Trans. Nanotechnol. 4, 284 (2005).

- <sup>18</sup>A. Vijayaraghavan, S. Kar, C. Soldano, S. Talapatra, O. Nalamasu, and P. M. Ajayan, Appl. Phys. Lett. 89, 162108 (2006).

- <sup>19</sup>H. Lin and S. Tiwari, Appl. Phys. Lett. 89, 073507 (2006).

- <sup>20</sup>A. Gruneis, M. J. Esplandiu, D. Garcia-Sanchez, and A. Bachtold, Nano Lett. 7, 3766 (2007).

- <sup>21</sup>D. Estrada, S. Dutta, A. Liao, and E. Pop, Nanotechnology **21**, 085702 (2010).

- <sup>22</sup>J. Cao, Q. Wang, D. Wang, and H. Dai, Small 1, 138 (2005).

- <sup>23</sup>J. Cao, Q. Wang, M. Rolandi, and H. Dai, Phys. Rev. Lett. 93, 216803 (2004).

- <sup>24</sup>W. Kim, A. Javey, O. Vermesh, Q. Wang, Y. Li, and H. Dai, Nano Lett. 3, 193 (2003).

- <sup>25</sup>Y. Pascal-Levy, E. Shifman, M. Pal-Chowdhury, I. Kalifa, T. Rabkin, O. Shtempluck, A. Razin, V. Kochetkov, and Y. E. Yaish, Phys. Rev. B 86, 115444 (2012).

- <sup>26</sup>Y. Pascal-Levy, E. Shifman, I. Sivan, I. Kalifa, M. Pal-Chowdhury, O. Shtempluck, A. Razin, V. Kochetkov, and Y. E. Yaish, J. Appl. Phys. **112**, 084329 (2012).

- <sup>27</sup>Y. Pascal-Levy, E. Shifman, M. Pal-Chowdhury, E. M. Hajaj, O. Shtempluck, A. Razin, V. Kochetkov, and Y. E. Yaish, ChemPhysChem 13, 4202 (2012).

- <sup>28</sup>M. Ganzhorn, A. Vijayaraghavan, S. Dehm, F. Hennrich, A. A. Green, M. Fichtner, A. Voigt, M. Rapp, H. von Lhneysen, M. C. Hersam, M. M. Kappes, and R. Krupke, ACS Nano 5, 1670 (2011).

- <sup>29</sup>T. Sharf, J. W. Kevek, T. DeBorde, J. L. Wardini, and E. D. Minot, Nano Lett. **12**, 6380 (2012).

- <sup>30</sup>S. Kar, A. Vijayaraghavan, C. Soldano, S. Talapatra, R. Vajtai, O. Nalamasu, and P. M. Ajayan, Appl. Phys. Lett. **89**, 132118 (2006).

- <sup>31</sup>M. Muoth, T. Helbling, L. Durrer, S.-W. Lee, C. Roman, and C. Hierold, Nat. Nanotechnol. 5, 589 (2010).

- <sup>32</sup>Z. Liu, H. Li, Z. Qiu, S.-L. Zhang, and Z.-B. Zhang, Adv. Mater. **24**, 3633 (2012).

- <sup>33</sup>T.-J. Ha, D. Kiriya, K. Chen, and A. Javey, ACS Appl. Mater. Interfaces 6, 8441 (2014).

- <sup>34</sup>J. Cao, S. T. Bartsch, and A. M. Ionescu, ACS Nano 9, 2836 (2015).

- <sup>35</sup>See supplementary material at http://dx.doi.org/10.1063/1.4947099 for two additional figures presenting the transfer characteristics in logarithmic scale and a contour map of the conductance within the global-local gates plan.

- plan. <sup>36</sup>Y. Taur and T. Ning, *Fundamental of Modern VLSI Devices* (Cambridge University, Cambridge, 1998).

- <sup>37</sup>K. Vanheusden, W. L. Warren, R. A. B. Devine, D. M. Fleetwood, J. R. Schwank, M. R. Shaneyfelt, P. S. Winokur, and Z. J. Lemnios, Nature 386, 587 (1997).

- <sup>38</sup>S. Tiwari, F. Rana, H. Hanafi, A. Hartstein, E. F. Crabbe, and K. Chan, Appl. Phys. Lett. 68, 1377 (1996).